|

19 Jan 2006

% cat RTLinv.sp

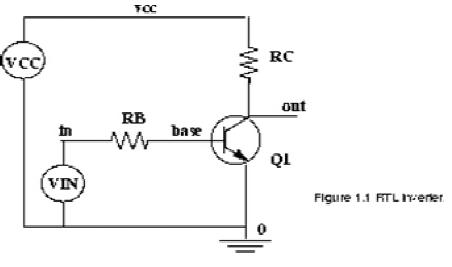

Simple RTL Inverter

.include ‘~ee141/MODELS/npn.mod’

*netlist---------------------------------------

VCC vcc 0 5

VIN in 0 PULSE 0 5 2NS 2NS 30NS 60NS

RB in base 10k

Q1 out base 0 NPN

RC vcc out 1k

*extra control information---------------------

.options post=2 nomod

.op

*analysis--------------------------------------

.TRAN 1ns 30ns

.DC VIN 0 5 0.1

.END

% hspice RTLinv.sp >! RTLinv.out

****** HSPICE -- V-2004.03 (20040116) 07:59:51

01/19/2006 solaris

Copyright (C) 2004 Synopsys, Inc. All Rights Reserved.

Unpublished-rights reserved under US copyright laws.

This program is protected by law and is subject to the

terms and conditions of the license agreement found in:

/share/instsww/synopsys/hspice//2004.03/license.txt

Use of this program is your acceptance to be bound by this

license agreement. HSPICE is the trademark of Synopsys, Inc.

Input File: RTLinv.sp

lic:

lic: FLEXlm: v6.1g

lic: USER: billhung HOSTNAME: cory.EECS.Berkeley.EDU

lic: HOSTID: 80c49828 PID: 19751

lic: Using FLEXlm license file:

lic: /share/instsww/synopsys/Univ_Tools/adm/license.dat

lic: Checkout hspice; Encryption code: 9D63921728E3C8C946A3

lic: License/Maintenance for hspice will expire on 28-sep-2006/2005.09

lic: 1(in_use)/50 FLOATING license(s) on SERVER

lic:

.include '/home/ff/ee141/models/npn.mod'

.model npn npn bf=100 is=1e-17 re=20 rc=75 rb=120 cje=20ff cjc=22ff cjs=47ff

+ vaf=50v

* netlist

vcc vcc 0 5

vin in 0 pulse 0 5 2ns 2ns 2ns 30ns 60ns

rb in base 10k

q1 out base 0 npn

rc vcc out 1k

*extra control information

.options post=2 nomod

.op

* analysis

.tran 1ns 30ns

.dc vin 0 5 .1

.end

Opening plot unit= 15

file=./RTLinv.sw0

1 ****** HSPICE -- V-2004.03 (20040116) 07:59:51 01/19/2006 solaris

******

simple rtl inverter

****** operating point information tnom= 25.000 temp= 25.000

******

***** operating point status is all simulation time is 0.

node =voltage node =voltage node =voltage

+0:base = 50.0001n 0:in = 0. 0:out = 5.0000

+0:vcc = 5.0000

**** voltage sources

subckt

element 0:vcc 0:vin

volts 5.0000 0.

current -5.0000p 5.0000p

power 25.0001p 0.

total voltage source power dissipation= 25.0001p watts

**** resistors

subckt

element 0:rb 0:rc

r value 10.0000k 1.0000k

v drop -50.0001n 5.0000n

current -5.0000p 5.0000p

power 2.500e-19 2.500e-20

**** bipolar junction transistors

subckt

element 0:q1

model 0:npn

ib -10.0000a

ic 21.0000a

vbe 50.0001n

vce 5.0000

vbc -5.0000

vs -5.0000

power 105.0001a

betad -2.1000

gm 425.7523a

rpi 2.569e+17

rx 120.0000

ro 4.166e+17

cpi 20.0000f

cmu 11.2332f

cbx 0.

ccs 16.9744f

betaac 109.3834

ft 2.1593m

Opening plot unit= 15

file=./RTLinv.tr0

***** job concluded

1 ****** HSPICE -- V-2004.03 (20040116) 07:59:51 01/19/2006 solaris

******

simple rtl inverter

****** job statistics summary tnom= 25.000 temp= 25.000

******

total memory used 157 kbytes

# nodes = 8 # elements= 5

# diodes= 0 # bjts = 1 # jfets = 0 # mosfets = 0

analysis time # points tot. iter conv.iter

op point 0.01 1 7

dc sweep 0.03 51 132

transient 0.03 31 142 37 rev= 7

readin 0.03

errchk 0.01

setup 0.00

output 0.00

total cpu time 0.21 seconds

job started at 07:59:51 01/19/2006

job ended at 07:59:52 01/19/2006

lic: Release hspice token(s)

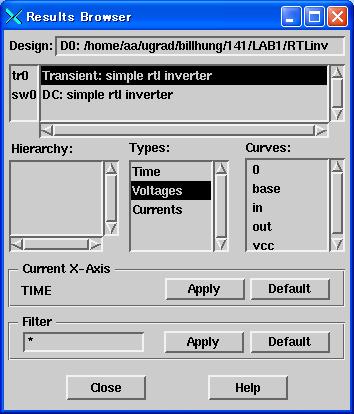

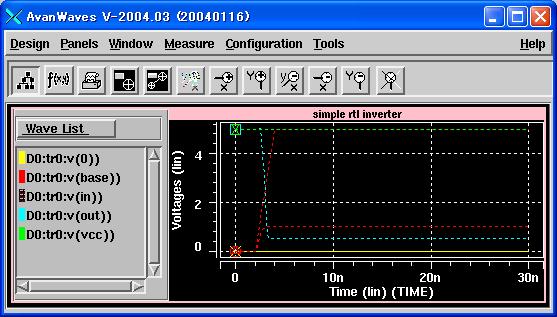

% awaves &

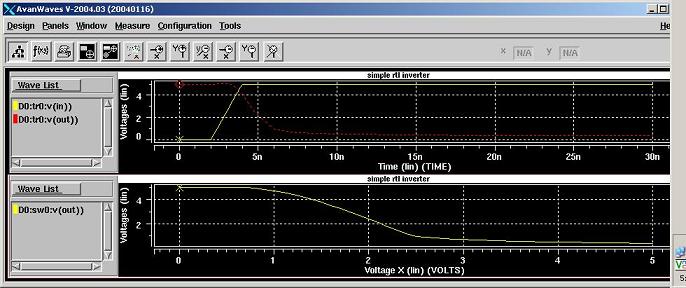

//and open RTLinv.sp, click Transient: simple rtl inverter ->

Voltage -> in, out

Open a new panel for the DC waveform by clicking on Panels/Add. Return to the

Results Browser or reopen by clicking Tools/Results Browser. Click on DC: Simple

RTL Inverter and repeat part f) to view the DC waveforms.

A model for the MOSFET must first be obtained. Replace npn.mod with scmos.mod in

the .include line of the your netlist and save as MOSinv.sp.

Edit MOSinv.sp by replacing the BJT with a MOSFET in your netlist.

Delete: Q1 out base 0 npn

Replace with: M1 out base 0 0 NMOS L=2u W=100u

|